# *ThermalTronix* TT-1640CLD-DS

# Long Wave Infrared Focal Plane Array

640×480 25um Uncooled Microbolometer

Issue D

# **Product Highlights**

- a-Si microbolometer

- 640×480 focal plane array

- Pixel pitch 25um by 25um

- Hermetic Vacuum package

- Room temperature operation with TEC

- Military standard qualification

- On-chip temperature sensor

- Frame rate 25Hz $\sim$ 50Hz

- Single or double analog output

- Frame size selectable

- Image flip controllable

- Gain control selectable

Intellisystem Technologies S.r.l.

# Contents

| Issue D1                     |

|------------------------------|

| Figure Lists                 |

| Glossary                     |

| 1 INTRODUCTION               |

| 2 STRUCTURAL OVERVIEW        |

| 3 PERFORMANCE SPECIFICATIONS |

| 4 ELECTRICAL INTERFACE       |

| 5 ENVIRONMENTAL CONDITIONS14 |

| 6 DELIVERY                   |

| 7 APPENDIX                   |

Intellisystem Technologies S.r.l.

Via Augusto Murri, 1 – 96100 Siracusa - Phone +39 (0)931-1756256 / +39 (0)2-87167549 - Mobile (+39) 335 1880035 em@il: info@intellisystem.it WEB: http://www.intellisystem.it

### Table Lists

| TABLE 1 Detector Pin List               | 6  |

|-----------------------------------------|----|

| TABLE 2 Bias Requirements For The TEC   | 7  |

| TABLE 3 Getter Re-activation Conditions | 7  |

| TABLE 4 Operability Specification       | 8  |

| TABLE 5 Operation Bias Conditions       |    |

| TABLE 6 Pulse Voltages                  | 10 |

| TABLE 7 Serial Link Instruction         |    |

| TABLE 8 Output Mode Control             | 12 |

| TABLE 9 CTIA Gain Control               | 12 |

| TABLE 12 Outputs                        | 13 |

| TABLE 13 Environment Conditions         | 14 |

## **Figure Lists**

| FIGURE 1 Detector Pin-out Diagram                               | 6  |

|-----------------------------------------------------------------|----|

| FIGURE 2 Typical temperature sensor output TOUT characteristics | 7  |

| FIGURE 3 Clock Diagram                                          | 10 |

| FIGURE 4 MCLK、 SERDAT Timing Diagram                            | 12 |

## Glossary

| Compatible Metal Oxide Semiconductor    |

|-----------------------------------------|

| Capacitance Trans-Impedance Amplifier   |

| Electrical Static Discharge             |

| Focal Plane Array                       |

| Infrared                                |

| Long Wave Infrared                      |

| Micro-Electro-Mechanical Systems        |

| Not Connected                           |

| Noise Equivalent Temperature Difference |

| Read Out Integrated Circuit             |

| Thermo-Electric Cooler                  |

|                                         |

Intellisystem Technologies S.r.l.

#### 1 INTRODUCTION

This document describes the operation conditions and main performance specifications of an uncooled long wave infrared focal plane array detector with reference number of **TT-1640CLD-DS**.

The **TT-1640CLD-DS** infrared detector is based on CMOS-MEMS micro-bolometer technology. The detector is a 640×480 pixels array with pixel pitch of 25um by 25um. The detector is sensitive to the long-wave infrared (LWIR) spectral range of 8um $\sim$ 14um.

The **TT-1640CLD-DS** infrared detector is vacuum packaged with an incorporated non-evaporable getter to maintain long-term vacuum. The temperature of the detector is controlled with a thermo-electric cooler (TEC). The **TT-1640CLD-DS** infrared detector is read-out row-by-row and can provide a single or a double analog output signal. The detector is typically operated under 25Hz $\sim$ 50Hz frame rate.

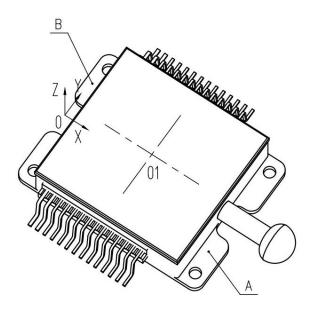

#### 2 STRUCTURAL OVERVIEW

The **TT-1640CLD-DS** detector consists of following physical structures: hermetic sealed vacuum metal packaging, an IR filter window in the front of the packaging, a non-evaporable getter inside of the packaging to help maintain long-term vacuum level, the FPA chip with an integrated temperature sensor, a thermo-electric cooler (TEC) to stabilize the detector temperature.

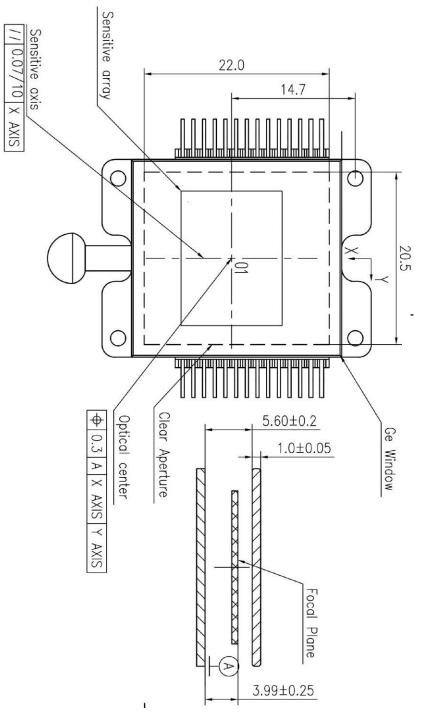

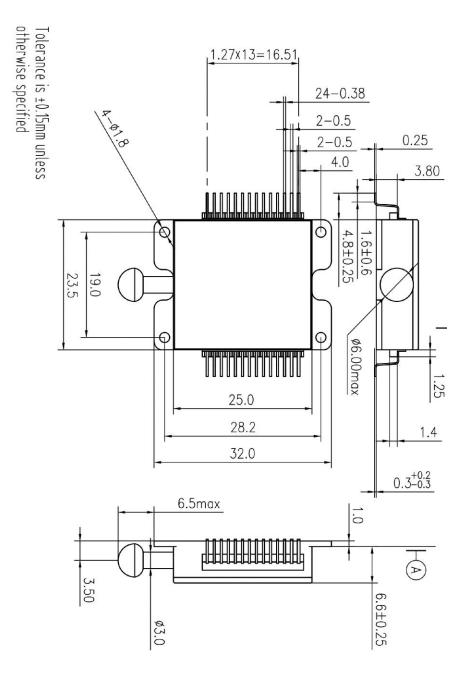

#### 2.1 Overall Dimensions

The physical structure and overall dimensions of the detector packaging are described in the Appendix (sheet A to C).

#### 2.2 Pin-out Diagram and List

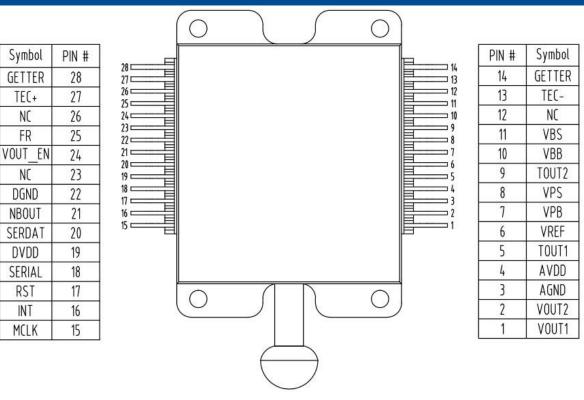

The pin-out diagram is presented in Figure 1, and the function of each pin is described in Table 1.

#### 2.3 Infrared Filter

An infrared filter window is incorporated in the front side of the detector package.

The outline size of the IR filter is 25.0mm by 23.5mm, its thickness is 1.0mm, The optical interface detail is described in the Appendix (sheet C).

#### Intellisystem Technologies S.r.l.

FIGURE 1 Detector Pin-out Diagram

Intellisystem Technologies S.r.l.

| Pin Nr | Symbol | Function              |   | Pin Nr | Pin Nr Symbol |

|--------|--------|-----------------------|---|--------|---------------|

| 1      | VOUT1  | Video analog output 1 |   | 15     | 15 MCLK       |

| 2      | VOUT2  | Video analog output 2 |   | 16     | 16 INT        |

| 3      | AGND   | Analog ground         |   | 17     | 17 RST        |

| 4      | AVDD   | Analog supply         |   | 18     | 18 SERIAL     |

| 5      | TOUT1  | Temperature sensor 1  |   | 19     | 19 DVDD       |

| 5      | VREF   | Reference voltage     |   | 20     | 20 SERDAT     |

| 7      | VPB    | Pixel biasing         |   | 21     | 21 NBOUT      |

| 3      | VPS    | Pixel ground          |   | 22     | 22 DGND       |

| Ð      | TOUT2  | Temperature sensor 2  |   | 23     | 23 NC         |

| 10     | VBB    | Blind pixel biasing   |   | 24     | 24 VOUT_EN    |

| 11     | VBS    | Blind pixel supply    |   | 25     | 25 FR         |

| 12     | NC     | Not connected         |   | 26     | 26 NC         |

| 13     | TEC-   | TEC-                  |   | 27     | 27 TEC+       |

| 14     | GETTER | Getter                | 2 | 8      | 8 GETTER      |

#### TABLE 1 Detector Pin List

Note: the NC pins can NOT be connected to any signal bus such as the ground etc.

#### 2.4 Thermo-Electric Cooler

#### TABLE 2 Bias Requirements For The TEC

| Pin Nr | Symbol | Absolute Max Rating         |

|--------|--------|-----------------------------|

| 13     | TEC-   | Voltage: 4.3V Current: 3.0A |

| 27     | TEC+   | Power: 7.0W                 |

The temperature stabilization is required to be 10mK.

The stabilized temperature of the detector is typically set 10K  $\sim$  20K above the ambient temperature.

#### Intellisystem Technologies S.r.l.

Via Augusto Murri, 1 – 96100 Siracusa - Phone +39 (0)931-1756256 / +39 (0)2-87167549 - Mobile (+39) 335 1880035 em@il: info@intellisystem.it WEB: http://www.intellisystem.it

2.5 Temperature Sensor

Two CMOS temperature sensors are integrated in the FPA ROIC chip, and two separate analog output TOUT1 and TOUT2 are provided, the function of the two TOUT are equivalent, each one can be used to control the TEC (the other should be electrically floating, can NEVER be connected to the ground).

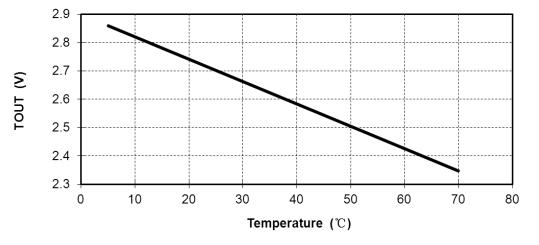

A typical TOUT versus the detector chip temperature relationship is shown in Figure 2. The sensitivity of the temperature sensor is about -7.85 mV/K. TOUT is about 2.70 V for an FPA temperature of 25°C.

#### FIGURE 2 Typical temperature sensor output TOUT characteristics

#### 2.6 Vacuum and Getter

The **TT-1640CLD-DS** detector is required to operate under high vacuum condition. A non-evaporable getter is integrated in the packaging to maintain the long-term vacuum level. The getter can be electrically re-activated when the performance of the detector is degraded due to the vacuum level degradation. The getter activation is performed by supplying a constant current to the two pins of the getter as shown in Table 3. Re-active the getter by the customer is not recommended.

TABLE 3 Getter Re-activation Conditions

| Pin Nr | Symbol | Current   | Time  |

|--------|--------|-----------|-------|

| 14/28  | Getter | 2.0A±0.1A | 10min |

#### Intellisystem Technologies S.r.l.

2.7 Weight

The total weight of the TT-1640CLD-DS detector is less than 20g.

2.8 Operating Temperature

The operating temperature range of the **TT-1640CLD-DS** detector is from  $-40^{\circ}$ C to  $+60^{\circ}$ C. A heat sink condition with typical thermal resistance of 4K/W is required between the packaging base plate and the ambient, especially when the detector is operated at the high end of the temperature range.

2.9 Storage Temperature

The storage temperature range of the **TT-1640CLD-DS** detector is from -40°C to +85°C.

#### **3 PERFORMANCE SPECIFICATIONS**

A detector test report is provided with each delivered detector by the manufacturer which contains testing results of the responsivity, temporal NETD and operability.

The definitions of several parameters are further explained as following.

3.1 Responsivity

The detector responsivity is not a fixed performance specification parameter, the value supplied the test report is a measured value under the certain biasing and test conditions.

- 3.2 Operability specification

- 3. 2. 1 Non-operating pixel

A pixel is defined as a "non-operating" if:

- its responsivity is less than 0.8x average responsivity or larger than 1.2x average responsivity;

- its NETD is larger than 1.5x average NETD;

- 3. 2. 2 Non-operating Row

A row is considered as non-operating if larger than 50% of the pixels are non-operating.

3. 2. 3 Non-operating Column

A column is considered as non-operating if larger than 50% of the pixels are non-operating.

3. 2. 4 Operability Specification

The operability of the delivered detector should meet the requirement in Table 4.

#### Intellisystem Technologies S.r.l.

#### TABLE 4 Operability Specifications

| Non-operating row or column | 0    |

|-----------------------------|------|

| Non-operating pixels        | ≤1%  |

| Operability                 | ≥99% |

#### 4 ELECTRICAL INTERFACE

#### 4.1 Operation Bias Voltages

To properly operate the **TT-1640CLD-DS** detector, various bias voltages should be supplied to each pin as specified in Table 5.

| Pin<br>Nr | Symbol | Bias Type |         | ymbol Bias Ty               |       | Optimum<br>Value | Range                                               | Max<br>Current | Max RMS Noise |

|-----------|--------|-----------|---------|-----------------------------|-------|------------------|-----------------------------------------------------|----------------|---------------|

| 3         | AGND   | Input     | Fixed   | 0V                          | _     | 60mA             | _                                                   |                |               |

| 4         | AVDD   | Input     | Fixed   | 5V±100mV                    | _     | 60mA             | 2uV(1Hz~1KHz)<br>5uV(1Hz~10KHz)<br>100uV(1Hz~10MHz) |                |               |

| 6         | VREF   | Input     | Fixed   | 2.4V±25mV                   | _     | 1mA              | <100uV                                              |                |               |

| 7         | VPB    | Input     | Tunable | Given in the<br>test report | 2V~5V | 100uA            | 2uV(1Hz~1KHz)<br>5uV(1Hz~10KHz)<br>100uV(1Hz~10MHz) |                |               |

| 8         | VPS    | Input     | Fixed   | 0V                          | _     | 5mA              | -                                                   |                |               |

| 10        | VBB    | Input     | Fixed   | 1.7V                        | _     | 100uA            | 2uV(1Hz~1KHz)<br>5uV(1Hz~10KHz)<br>100uV(1Hz~10MHz) |                |               |

| 11        | VBS    | Input     | Tunable | Given in the<br>test report | 2V~5V | 5mA              | 2uV(1Hz~1KHz)<br>5uV(1Hz~10KHz)<br>100uV(1Hz~10MHz) |                |               |

| 19        | DVDD   | Input     | Fixed   | 5V±300mV                    | _     | 10mA             | <100mV                                              |                |               |

| 22        | DGND   | Input     | Fixed   | 0V                          | _     | 10mA             | _                                                   |                |               |

#### TABLE 5 Operation Bias Conditions

$\mathsf{VPB}_{\mathsf{v}}$   $\mathsf{VBS}$  can be adjusted to optimize the detector performance within the above range

Note : Special Requirements for Supplying the Bias Voltages (the detector could severely damage if the following instructions are not followed):

Intellisystem Technologies S.r.l.

Via Augusto Murri, 1 – 96100 Siracusa - Phone +39 (0)931-1756256 / +39 (0)2-87167549 - Mobile (+39) 335 1880035 em@il: info@intellisystem.it WEB: http://www.intellisystem.it

1) When supply the bias voltages , it is required that the VPB is supplied last, when all the other signals and bias

have been supplied and stabilized;

- 2) When power off the detector, it is required that the VPB is turned off first, all the other signals and bias voltage can be turned off only after the VPB has been off;

- 3) If need to change SERDAT input to achieve serial link control then the detector is actively biased, it is required to turn the VPB signal off firstly, then change SERDAT, and turn on the VPB again.

4.2 Pulse Voltage and Clock Diagram

| Pin | Cumb al | Pulse Type |        |       | Low Level |      |      | High Level |      |

|-----|---------|------------|--------|-------|-----------|------|------|------------|------|

| Nr  | Symbol  | Puis       | етуре  | Min   | Typical   | Max  | Min  | Typical    | Max  |

| 15  | MCLK    | Input      | 5V TTL | -0.3V | 0V        | 0.3V | 4.7V | 5V         | 5.5V |

| 16  | INT     | Input      | 5V TTL | -0.3V | 0V        | 0.3V | 4.7V | 5V         | 5.5V |

| 17  | RST     | Input      | 5V TTL | -0.3V | 0V        | 0.3V | 4.7V | 5V         | 5.5V |

| 20  | SERDAT  | Input      | 5V TTL | -0.3V | 0V        | 0.3V | 4.7V | 5V         | 5.5V |

TABLE 6 Pulse Voltages

Intellisystem Technologies S.r.l.

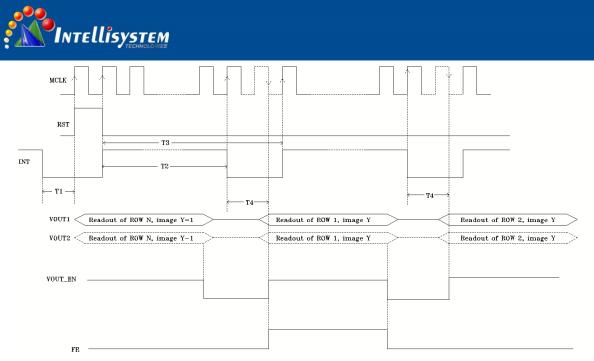

T1>15TMCLK, 15TMCLK<T2(Integration time)<640 TMCLK, T3>(640+17)TMCLK, T4=18.5TMCLK

FIGURE 3 Clock Diagram for 640×480 Configuration

4.3 Serial Control

The serial control bus is developed for infrared imagers. The serial link (SERDAT: PIN #20) is used to write the required user data. And SERIAL (PIN #18) commands the serial link (SERDAT).

#### 4.3.1 SERIAL

4.3.1.1 SERIAL=OV

When SERIAL=OV, SERDAT is off , only NBOUT (PIN #21) is available.

- a) When NBOUT=0V, double analog output: VOUT1 and VOUT2;

- b) When NBOUT=5V, single analog output: only VOUT1;

- c) CTIA capacitance is fixed to 18pF.

#### 4.3.1.2 SERIAL=5V

When SERIAL=5V, SERDAT is available, and NBOUT (PIN #21) is off.

- a) When SERDAT=0V, only VOUT1 single analog output, CTIA capacitance is fixed to 18pF;

- b) When SERDAT is defined by 4.3.2, all the functions given by the serial link are available.

- 4. 3. 2 Serial Control Bus

SERDAT (PIN #20) is a 51 bits control signal defined as in Table 7. The main feature of the serial interface

include:

a) Single analog output or double analog output: NBOUT

#### Intellisystem Technologies S.r.l.

Via Augusto Murri, 1 – 96100 Siracusa - Phone +39 (0)931-1756256 / +39 (0)2-87167549 - Mobile (+39) 335 1880035 em@il: info@intellisystem.it WEB: http://www.intellisystem.it

- b) CTIA gain value: GAIN

- c) Image flip: HFLIP  $\$  VFLIP

- d) Windowing: SIZEA、SIZEB

SERDAT can be applied by each frame or just once.

To activate the serial control bus, the first bit named START needs to be set at "1" i.e high level.

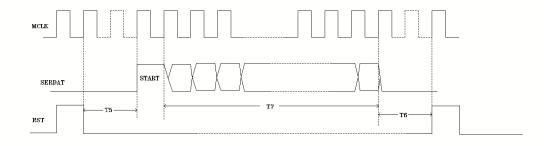

The clock frequency of SERDAT is governed by the Master Clock (MCLK). Data will be taken into account if START bit is at high level. Data must change during rising edge of MCLK and will be taken into account at the falling edge of the next RST. The timing diagram of SERDAT is shown in Figure 4.

|          | Length          |                    | Format                  |       | Example           |  |

|----------|-----------------|--------------------|-------------------------|-------|-------------------|--|

| Position | (in bit number) | Name               | Name (binary/decimal) V |       | Binary conversion |  |

| 1        | 1               | START              | binary                  | 1     | 1                 |  |

| 2        | 1               | Reserved           | binary                  | 0     | 0                 |  |

| 3        | 3               | Reserved           | binary                  | 0,0,0 | 000               |  |

| 4        | 1               | NBOUT              | binary                  | 1     | 1                 |  |

| 5        | 3               | GAIN               | binary                  | 1,1,1 | 111               |  |

| 6        | 1               | HFLIP              | binary                  | 1     | 1                 |  |

| 7        | 1               | VFLIP              | binary                  | 1     | 1                 |  |

| 8        | 1               | SIZE-A             | binary                  | 1     | 1                 |  |

| 9        | 1               | SIZE-B             | binary                  | 0     | 0                 |  |

| 10       | 9               | Y <sub>first</sub> | Decimal                 | 320   | 101000000         |  |

| 11       | 9               | Y <sub>last</sub>  | Decimal                 | 160   | 010100000         |  |

| 12       | 10              | X <sub>first</sub> | Decimal                 | 160   | 0010100000        |  |

| 13       | 10              | X <sub>last</sub>  | Decimal                 | 320   | 0101000000        |  |

TABLE 7 Serial Link Instruction

T5≥1TMCLK, T6≥1TMCLK, T7=50TMCLK

FIGURE 4 SERDAT Timing Diagram

#### 4. 3. 2. 1 NBOUT

The following table gives the output mode versus NBOUT value.

Intellisystem Technologies S.r.l.

TABLE 8 Output Mode Control

| NBOUT | Output mode             |

|-------|-------------------------|

| 1     | Single-end (by default) |

| 0     | Double-end              |

#### 4. 3. 2. 2 Gain Control

The GAIN enable CTIA gain adaptation for specific operating conditions. The different avilable configurations are as following:

| Gain  | Value | CTIA Capacitance(pF) |

|-------|-------|----------------------|

| 1.00  | 111   | 18                   |

| 1.125 | 011   | 16                   |

| 1.29  | 101   | 14                   |

| 1.50  | 001   | 12                   |

| 1.80  | 110   | 10                   |

| 2.25  | 010   | 8                    |

| 3.00  | 100   | 6                    |

| 4.50  | 000   | 4                    |

#### TABLE 9 CTIA Gain Control

#### 4. 3. 2. 3 Image Flip

The image could be flipped in horizontal and vertical direction using HFLIP and VFLIP input, as described in Table 10.

| Scanning Direction | HFLIP | VFLIP |

|--------------------|-------|-------|

| right→left/up→down | 1     | 1     |

| right→left/down→up | 1     | 0     |

| left→right/up→down | 0     | 1     |

| left→right/down→up | 0     | 0     |

#### 4. 3. 2. 4 Windowing

Three different windows of interest are available: 648×488, 640×480 and 384×288 with the same optical center plus a user defined window determined by 2 opposite corner coordinates. The selection of the size is made by the serial link. The following table gives the size format versus the SIZEA and SIZEB values:

The user defined window need abide bellow rule(X-Y): Column defination:  $160 \le X \le 648$ ; Row defination:  $1 \le Y \le 488$ .

Intellisystem Technologies S.r.l.

Via Augusto Murri, 1 – 96100 Siracusa - Phone +39 (0)931-1756256 / +39 (0)2-87167549 - Mobile (+39) 335 1880035 em@il: info@intellisystem.it WEB: http://www.intellisystem.it

#### TABLE 11 Format Size Control

| FORMAT       | SIZEA | SIZEB |

|--------------|-------|-------|

| 648×488      | 1     | 1     |

| 640×480      | 1     | 0     |

| 384×288      | 0     | 1     |

| User Defined | 0     | 0     |

#### 4.4 Output Characteristics

The detector contains two type of outputs. VOUT1 and VOUT2 are the analog video output, TOUT1 and TOUT2 are the temperature sensor output. The outputs are described in Table 12.

#### TABLE 10 Outputs

| Pin Nr | Symbol | Output Type |          | Range     |

|--------|--------|-------------|----------|-----------|

| 1      | VOUT1  | Output      | variable | 0.4V~4.0V |

| 2      | VOUT2  | Output      | variable | 0.4V~4.0V |

| 5      | TOUT1  | Output      | variable | 2.0V~3.3V |

| 9      | TOUT2  | Output      | variable | 2.0V~3.3V |

#### **5** ENVIRONMENTAL CONDITIONS

**TT-1640CLD-DS** detector is GJB-qualified (MIL-STD equivalent). The detector qualification is performed on the basis of sampling from the manufactured products and is representative of the typical manufacturing technology level. The detector should be qualified to the climatic and mechanical environmental conditions as listed in Table 13.

#### Intellisystem Technologies S.r.l.

Via Augusto Murri, 1 – 96100 Siracusa - Phone +39 (0)931-1756256 / +39 (0)2-87167549 - Mobile (+39) 335 1880035 em@il: info@intellisystem.it WEB: http://www.intellisystem.it

#### TABLE 11 Environment Conditions

| Nr | ltem                     | Standard and Method  |

|----|--------------------------|----------------------|

| 1  | High temperature storage | GJB 1788 Method 2020 |

| 2  | Low temperature storage  | GJB 1788 Method 2040 |

| 3  | Thermal Shocks           | GJB 1788 Method 2010 |

| 4  | Random vibration         | GJB 1788 Method 2080 |

| 5  | Shocks                   | GJB 1788 Method 2070 |

#### 6 **DELIVERY**

#### 6.1 Packing

During transportation, the detector is placed into a plastic box and wedged with conductive foam, a testing report is delivered together with each detector.

#### 6.2 Storage

Detectors should be stored at conditions: temperature at -10°C $\sim$ 40°C, relative humidity is less than 70%, dry and non-corrosive environment.

6.3 General Recommendations

Specific care should be taken in handling the **TT-1640CLD-DS** detector:

- a) Electrostatic discharge (ESD) protection

- b) Avoid directing the detector directly towards the sun, especially in the case the detector is mounted with a lens

#### 7 APPENDIX

- a) Sheet A: General View

- b) Sheet B: Mechanical Interface

- c) Sheet C: Optical Interfa

#### Intellisystem Technologies S.r.l.

Via Augusto Murri, 1 – 96100 Siracusa - Phone +39 (0)931-1756256 / +39 (0)2-87167549 - Mobile (+39) 335 1880035 em@il: info@intellisystem.it WEB: http://www.intellisystem.it

#### Sheet A General View

#### NOTE:

- 1-Mechanical reference OXYZ are materialised by: XY: Mechanical Mounting surface (A plane) X: Symmetry axis of the structure Y: Perpendicular to X axis through line B

- Z: Normal to XY plane O: XYZ axis center

- 2-01: Optical plane center

#### Intellisystem Technologies S.r.l.

Sheet B Mechanical Interface

#### Intellisystem Technologies S.r.l.

#### Sheet C Optical Interface

#### Intellisystem Technologies S.r.l.

Via Augusto Murri, 1 – 96100 Siracusa - Phone +39 (0)931-1756256 / +39 (0)2-87167549 - Mobile (+39) 335 1880035 em@il: info@intellisystem.it WEB: http://www.intellisystem.it